De evolutie van PCIe-standaarden vormt de ruggengraat van moderne computerarchitectuur. Terwijl PCIe 4.0 eindelijk mainstream adoptie heeft bereikt, kondigt PCIe 5.0 zich aan als de volgende revolutionaire stap in interconnect-technologie. Met een theoretische bandbreedte die opnieuw verdubbelt, belooft PCIe 5.0 ongekende prestaties voor high-end workloads. Echter, deze technologische sprong brengt complexe engineering-uitdagingen met zich mee op het gebied van signaalintegriteit, power management en thermal design. Voor hardware-enthousiastelingen die werkelijk willen begrijpen wat deze transitie betekent, vereist het een grondige analyse van de onderliggende protocollen, elektrische specificaties en real-world implementatie-beperkingen die beide standaarden definiëren.

Bandbreedte-evolutie en protocol-optimalisaties

De fundamentele architectuur van PCIe 4.0 en 5.0 toont een interessante continuïteit in encoding-methodologie, waarbij beide standaarden de 128b/130b encoding hanteren die geïntroduceerd werd in PCIe 3.0. Deze encoding behoudt een efficiëntieratio van 98,46%, waarbij 128 bits nuttige data getransporteerd worden binnen een 130-bit frame. Het cruciale verschil ligt in de signaling rate: PCIe 4.0 opereert op 16 GT/s (gigatransfers per seconde), terwijl 5.0 deze verdubbelt naar 32 GT/s.

Deze verdubbeling van de signaling rate resulteert in een proportionele bandbreedte-toename. Een PCIe 4.0 x16 configuratie levert een theoretische bandbreedte van 15,75 GB/s, terwijl PCIe 5.0 x16 31,5 GB/s bereikt. Deze berekening volgt uit: (32 GT/s × 16 lanes × 128/130) ÷ 8 bits per byte = 31,5 GB/s.

De protocol-stack optimalisaties in PCIe 5.0 zijn essentieel voor het realiseren van deze theoretische prestaties. De verfijnde Credit-based flow control mechanismen introduceren dynamische buffer-allocatie op de Transaction Layer. Deze aanpassing voorkomt dat snellere transmissies leiden tot overflow-situaties bij ontvangende devices.

TLP (Transaction Layer Packet) processing onderging significante optimalisatie door verbeterde parallel processing-mogelijkheden. De packet-headers worden nu efficiënter geparsed, waarbij multiple TLP’s simultaan verwerkt kunnen worden. Dit reduceert de processing-overhead aanzienlijk bij high-throughput scenario’s.

DLLP (Data Link Layer Packet) handling profiteert van geoptimaliseerde acknowledgment-mechanismen. De ACK/NAK sequenties zijn gestroomlijnd om de round-trip latency te minimaliseren, cruciaal bij de hogere datarates van PCIe 5.0.

De scrambling polynomial aanpassingen in PCIe 5.0 verbeteren signaal-integriteit door elektromagnetische interferentie te reduceren. Het nieuwe polynomial spreidt spectrale energie uniformer, wat elektromagnetische compatibiliteit ten goede komt.

Real-world throughput wijkt significant af van theoretische maxima. NVMe SSD’s bereiken typisch 85-90% van de theoretische bandbreedte door overhead van het NVMe-protocol en controller-limitaties. High-end GPU’s zoals moderne gaming-videokaarten presteren vaak beter met 92-95% efficiency door geoptimaliseerde drivers en directe memory access.

Queue depth beïnvloedt prestaties exponentieel. Shallow queues (depth 1-4) resulteren in 40-60% throughput-degradatie door inadequate pipeline-utilization. Optimale prestaties vereisen queue depths van 32-128 voor storage-devices en 64-256 voor netwerk-adapters.

Block sizes tonen een logaritmische relatie met doorvoer. Kleine blocks (4KB) bereiken slechts 30-40% van de theoretische bandbreedte door protocol-overhead. Grotere blocks (64KB+) optimaliseren bandwidth-utilization naar 90%+.

Interrupt coalescing reduceert CPU-overhead door multiple completion-events te bundelen. Deze techniek kan throughput verhogen met 15-25% bij workloads met hoge I/O-frequenties, essentieel voor het realiseren van PCIe 5.0’s potentieel.

Signaalintegriteit en implementatie-complexiteit

De transitie naar PCIe 5.0’s verhoogde signaling rate van 32 GT/s brengt fundamentele uitdagingen met zich mee die de grenzen van conventionele interconnect-architectuur overschrijden. Bij deze frequenties wordt crosstalk tussen adjacente traces exponentieel kritischer, waarbij elektromagnetische interferentie significant kan toenemen. De insertion loss parameters verscherpen aanzienlijk, waardoor signaalverzwakking over langere PCB-traces problematisch wordt. Return loss specificaties worden stringenter, omdat reflecties bij hogere frequenties de signaalintegriteit drastisch kunnen beïnvloeden.

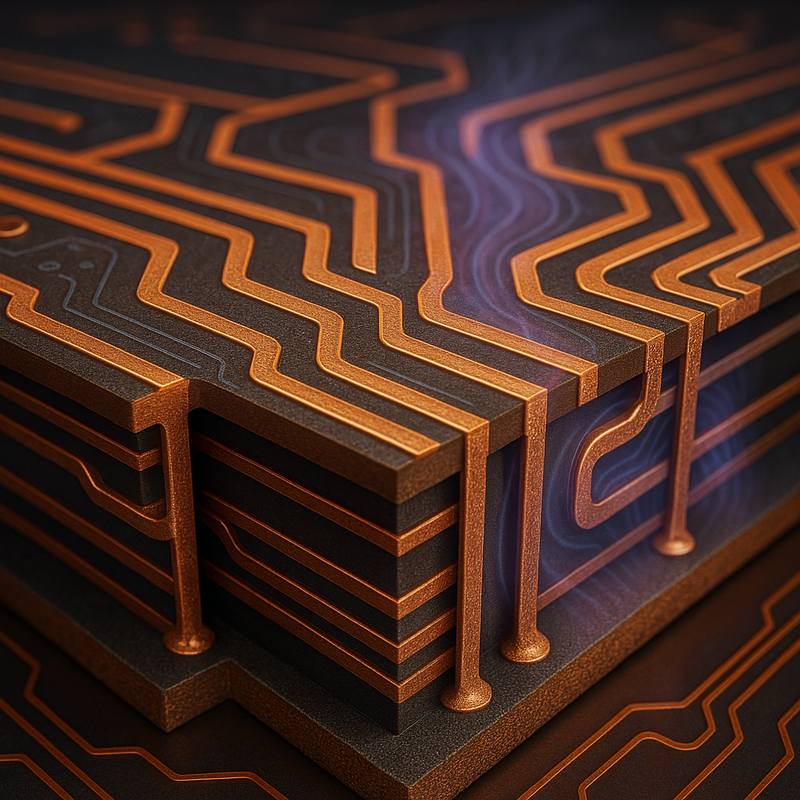

De Nyquist frequency implicaties bij 32 GT/s revolutioneren fundamenteel het PCB trace design. Traditionele routing-methodologie volstaat niet meer, waarbij gecontroleerde impedantie-matching en differentiële paarlengtes binnen micrometers nauwkeurig moeten zijn. PCB-ontwerpers moeten layer stackup optimaliseren met meer signaallagen en verbeterde diëlektrische materialen om signaalintegriteit te waarborgen.

Equalization-strategieën tussen PCIe 4.0 en 5.0 tonen aanzienlijke evolutie. PCIe 4.0 implementeert voornamelijk transmitter emphasis (Tx EQ) met statische pre-emphasis instellingen die tijdens initialisatie worden vastgesteld. Receiver equalization (Rx EQ) blijft relatief eenvoudig met beperkte adaptieve capaciteiten. PCIe 5.0 introduceert geavanceerde adaptive equalization algoritmes die real-time channel-condities monitoren en dynamisch aanpassen. Deze algoritmes analyseren continu channel operating margins en optimaliseren automatisch voor variërende omstandigheden.

Bit error rates (BER) vereisten voor PCIe 5.0 zijn stringenter dan 4.0, waarbij acceptable error rates verder omlaag gaan. Dit vereist robuustere error correction mechanismen en nauwkeurigere timing recovery circuits die complexiteit aanzienlijk verhogen.

Voor motherboard manufacturers ontstaan substantiële implementatie-uitdagingen. Via stitching technieken worden essentieel om ground plane continuïteit te handhaven bij hoghere frequenties. Traditionele via-structuren introduceren inductieve discontinuïteiten die bij 32 GT/s signaalintegriteit compromitteren. Retimers en redrivers worden onmisbaar voor PCIe 5.0 implementaties, vooral bij trace lengths boven 6 inch. Deze componenten regenereren signalen en compenseren voor channel losses, maar introduceren additional latency en power consumption.

Power delivery complexiteiten intensiveren door verhoogde switching frequencies. Moderne gaming PC builds vereisen nauwkeurigere power regulation en noise filtering. Thermal management wordt kritischer omdat hogere frequenties meer warmte genereren in switch-componenten en signaalprocessing circuits.

Cost implications beperken vroege 5.0 adoptie tot high-end platforms. Geavanceerde PCB-materialen, additional equalization hardware en strengere manufacturing toleranties verhogen productiekosten aanzienlijk. Motherboard manufacturers moeten investeren in nieuwe design tools en manufacturing processes, waarbij vroege implementaties voornamelijk beperkt blijven tot server-grade en premium enthusiast motherboards waar performance-premiums economisch gerechtvaardigd zijn.

PCIe 5.0 representeert een significante technologische evolutie die verder gaat dan simpele bandbreedte-verdubbeling. De complexe signaalintegriteit-uitdagingen, verhoogde implementatiekosten en thermische overwegingen maken vroege adoptie een premium-aangelegenheid. Voor hardware-enthousiastelingen betekent dit dat PCIe 4.0 voorlopig de sweet spot blijft voor mainstream toepassingen, terwijl 5.0 zijn waarde bewijst in gespecialiseerde workloads waar extreme I/O-prestaties kritisch zijn. De werkelijke revolutie ligt niet alleen in ruwe bandbreedte, maar in de engineering-innovaties die toekomstige interconnect-architecturen mogelijk maken.